# EE 505

# Lecture 24

# ADC Design – Pipeline

**Review from last lecture**

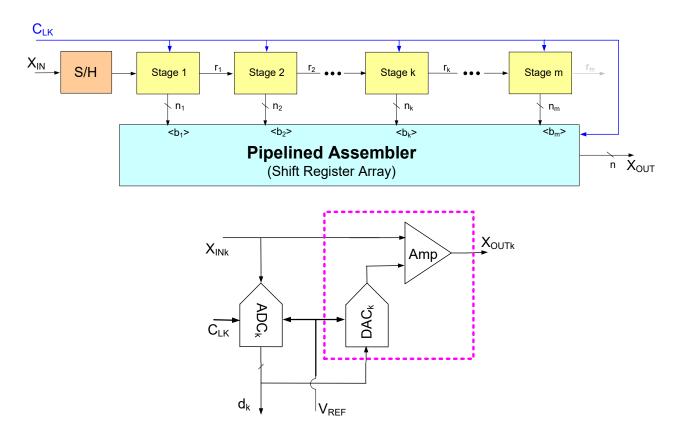

# Pseudo-Static Time-Invariant Modeling of a Linear Pipelined ADC

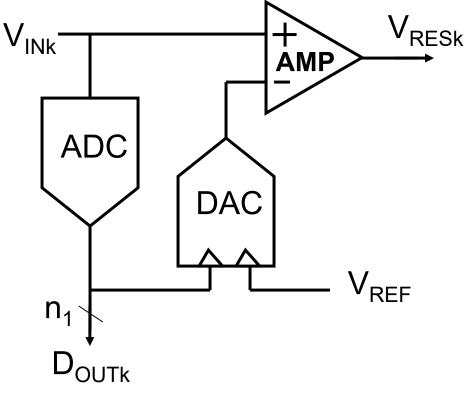

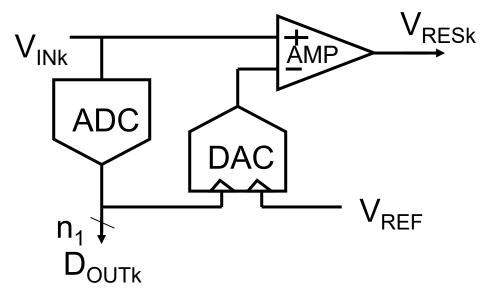

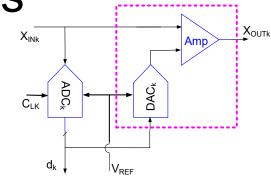

#### Parameterization of Stage k •Amplifier V<sub>INk</sub>- Closed-Loop Gain •From input – m1k •From DAC – m2k •From offset – m3k •Offset Voltage - V<sub>OSk</sub> •DAC •V<sub>DACki</sub> •ADC Offset Voltages - V<sub>OSAki</sub> •Out-Range Circuit (if used and not $n_1$ included in ADC/DAC) •DAC Levels - V<sub>DACBki</sub> •Amplifier Gain – m4k

#### Review from last lecture Solution of the 2n Linear Equations

$$V_{in} = \left\{ \frac{d_{1} \left[ \left( \frac{m_{21}}{m_{11}} \right) V_{DAC1} \right] + d_{2} \left[ \left( \frac{m_{22}}{m_{11}m_{12}} \right) V_{DAC2} \right] + ... + d_{n} \left[ \left( \frac{m_{2n}}{m_{11}m_{12}...m_{1n}} \right) V_{DACn} \right] + \frac{V_{REF}}{2^{n+1}} \right\}$$

$$\left\{ \frac{m_{31}}{m_{11}} V_{OS1} + \frac{m_{32}}{m_{11}m_{12}} V_{OS2} + ... + \left( \frac{m_{3n}}{m_{11}m_{12}...m_{1n}} \right) V_{OSn} \right\}$$

$$\left\{ \frac{V_{RESn}}{m_{11}m_{12}...m_{1n}} - \frac{V_{REF}}{2^{n+1}} \right\}$$

$$Code-independent offset term offset term$$

Note: Will not even include last residue amplifier nor create  $V_{RESn}$

Note: ADC errors do not affect linearity performance of pipelined structure but DAC outputs and weights are critical

Pseudo-Static Time-Invariant Modeling of a Linear Pipelined ADC

If more than 1 bit/stage is used and DAC is binarilyweighted structure

$$V_{_{RESk}} = m_{_{1k}}V_{_{ink}} + m_{_{2k}}\left(\sum_{_{j=1}^{2^{n_{k}}-1}}d_{_{kj}}V_{_{DACkj}}\right) + m_{_{3k}}V_{_{OSk}}$$

#### **Review from last lecture**

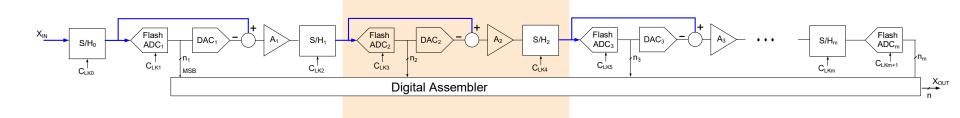

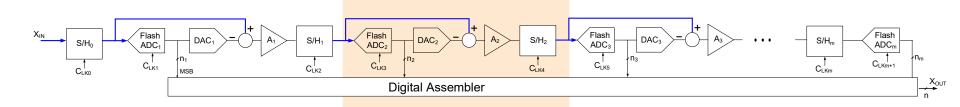

#### **Pipelined ADC**

Claim: If the Amplifiers are linear, settling is complete, and over-range protection is provided, the pipelined ADC makes no nonlinearity errors if the output of the DACs are correctly interpreted

Implication: Flash ADC errors, offsets in comparators and amplifiers, and gain errors in amplifier and S/H do not degrade linearity performance of a well-designed pipelined ADC structure !!

# Review from last lecture Observations

$$V_{in} = \sum_{k=1}^{n} \alpha_k d_k + f(\text{offset}) + f(\text{residue})$$

form of  $\alpha_k : V_{\text{DACk}} \frac{m_{2k}}{\prod_{j=1}^{k} m_{1j}}$

- Substantial errors are introduced if  $\alpha_k$  are not correctly interpreted!

- Some calibration and design strategies focus on accurately setting gains and DAC levels

- Analog calibration can be accomplished with either DAC level or gain calibration

- Digital calibration based upon coefficient identification does not require accurate gains or precise DAC levels

#### Review from last lecture Observations (cont)

$$V_{in} = \sum_{k=1}^{n} \alpha_k d_k + f(offset) + f(residue)$$

$\begin{array}{lll} \text{form of} & \alpha_k \, : \, V_{\text{DACk}} \frac{m_{2k}}{\displaystyle\prod_{j=1}^k m_{1j}} \end{array}$

- If nonlinearities are avoided, data conversion process with a pipelined architecture is extremely accurate

- Major challenge at low frequencies is accurately interpreting the digital output codes

#### Review from last lecture Observations (cont)

$$V_{in} = \sum_{k=1}^{n} \alpha_k d_k + f(offset) + f(residue)$$

$\begin{array}{lll} \text{form of} & \alpha_k \, : \, V_{\text{DACk}} \frac{m_{2k}}{\displaystyle\prod_{j=1}^k m_{1j}} \end{array}$

• If nonlinearities are present, this analysis falls apart and the behavior of the ADC is unpredictable !

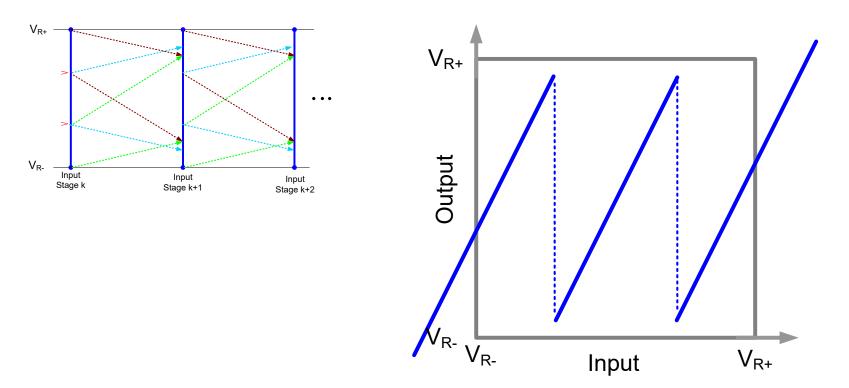

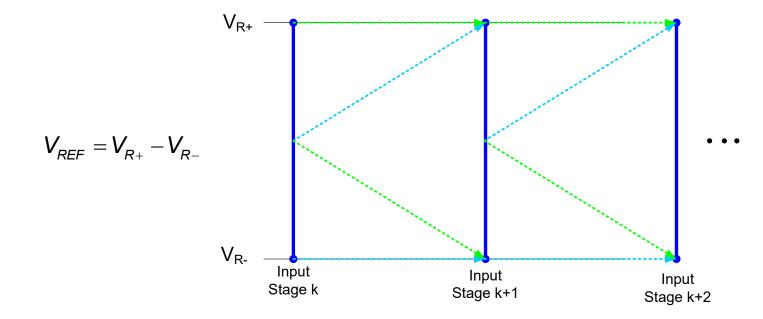

#### Intuitive View of Why Sub-ADCs do Not Cause Nonlinearity Errors

Claim: If the Amplifiers are linear, settling is complete, and over-range protection is provided, the pipelined ADC makes no nonlinearity errors if the output of the DACs are correctly interpreted

for 1 bit/stage

V,

$$_{n} = \left\{ d_{1} \left[ \left( \frac{m_{_{21}}}{m_{_{11}}} \right) V_{REF} \right] + d_{2} \left[ \left( \frac{m_{_{22}}}{m_{_{11}}m_{_{12}}} \right) V_{REF} \right] + \dots + d_{n} \left[ \left( \frac{m_{_{2n}}}{m_{_{11}}m_{_{12}}\dots m_{_{1n}}} \right) V_{REF} \right] + \frac{V_{REF}}{2^{n+1}} \right\} + V_{OSEQ} + \epsilon$$

- ADCs determine whether a quantity is or is not subtracted from  $V_{\text{REF}}$  at each stage but the DAC determines how much is subtracted

- Keep subtracting smaller-and-smaller quantities from V<sub>IN</sub> until residue is approx. 0 at end of last stage (and error caused by last sub-ADC will be small)

- If we know how much is subtracted from  $V_{IN}$  until residue vanishes, we know  $V_{IN}$

- Over-range protection recovers errors caused by subtracting too much or too little

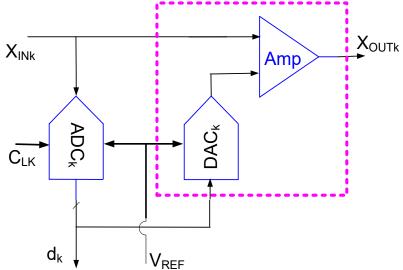

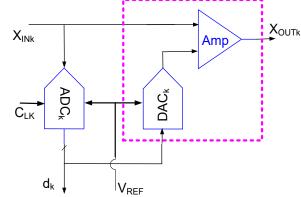

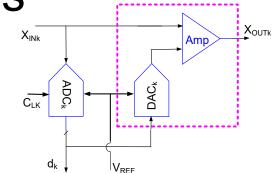

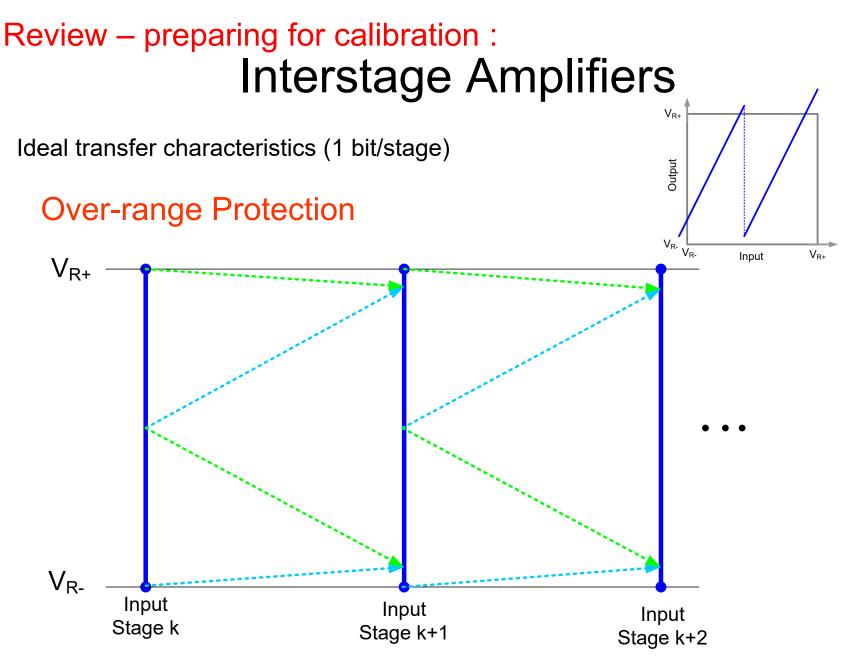

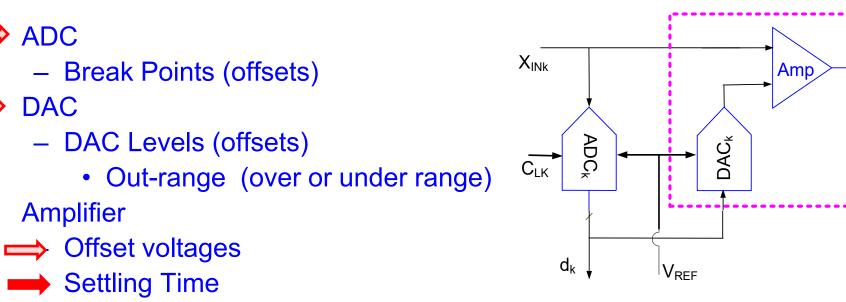

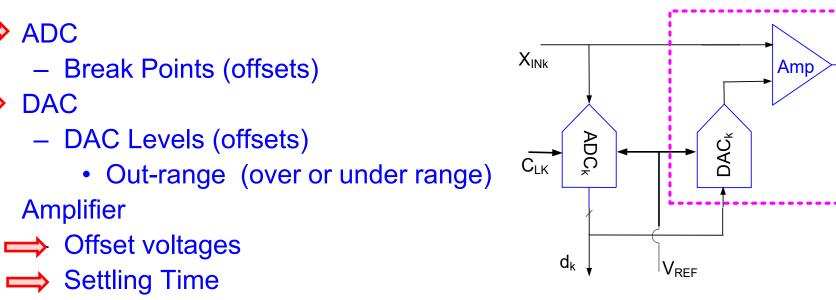

#### Performance Limitations of Pipelined ADCs (consider amplifier, ADC and DAC issues)

- XINk Break Points (offsets) DAC Levels (offsets)  $C_{LK}$  Out-range (over or under range) Amplifier

- Offset voltages

- Settling Time

ADC

DAC

- Nonlinearity (primarily open loop)

- Open-loop

- Out-range

- Gain Errors

- Inadequate open loop gain

- Component mismatch

- Power Dissipation

- kT/C switching noise

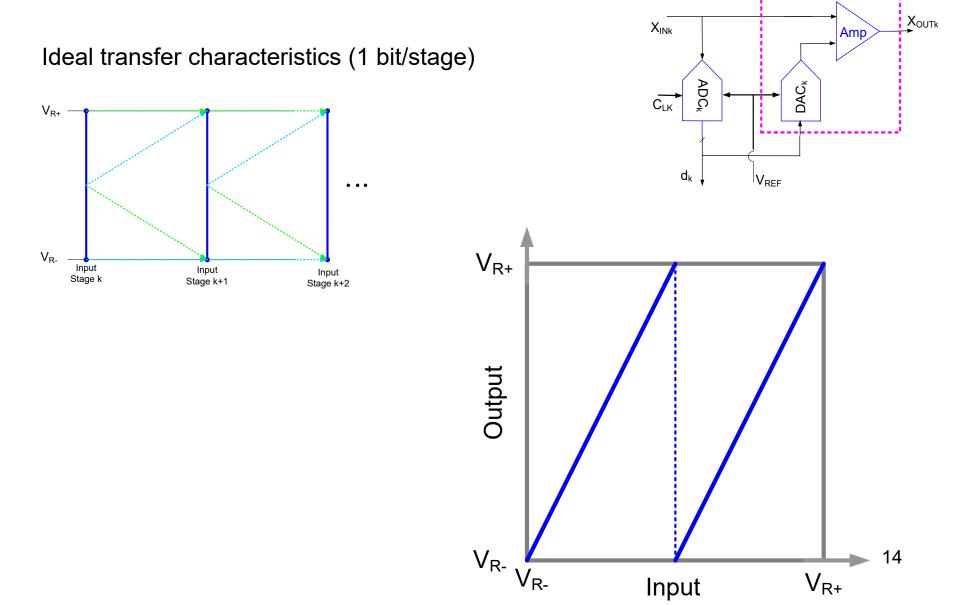

#### Performance Limitations of Pipelined ADCs (consider amplifier, ADC and DAC issues)

- Nonlinearity (primarily open loop)

- Open-loop

- 🔶 Out-range

- Gain Errors

- Inadequate open loop gain

- Component mismatch

- Power Dissipation

- kT/C switching noise

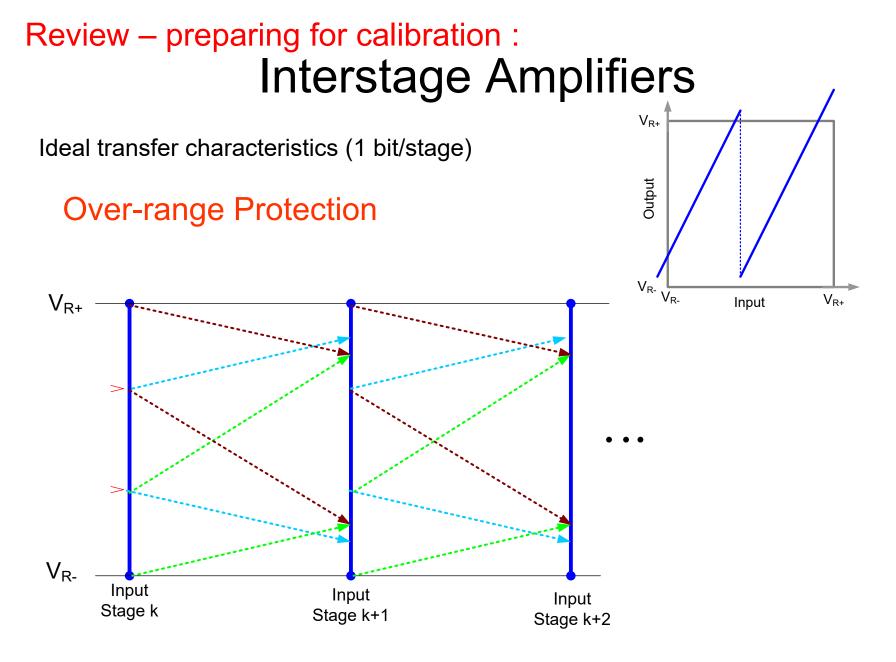

# Pipelined Data Converter Design Guidelines

#### Issue

#### Strategy

1. ADC offsets, Amp Offsets, Finite Op Amp Gain, DAC errors, Finite Gain Errors all cause amplifiers to saturate

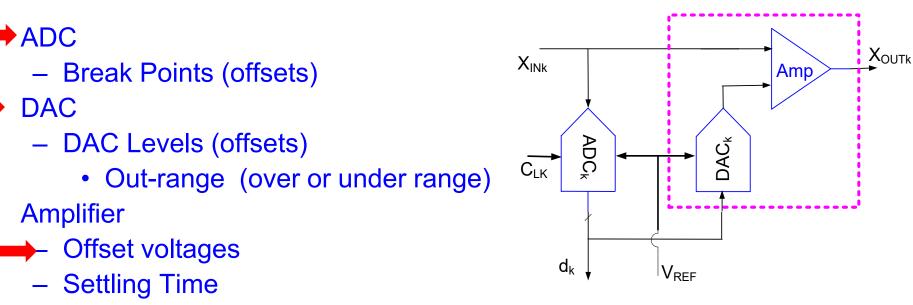

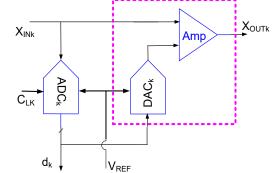

Typical Finite-Gain Inter-stage Amplifier (shown single-ended with 1-bit/stage)

13

#### But what really happens?

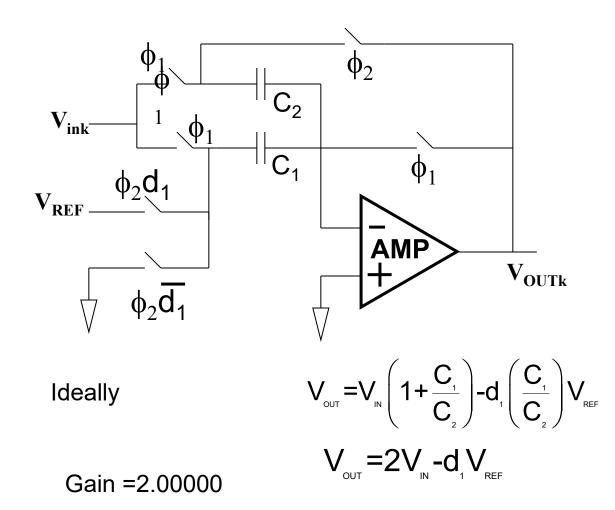

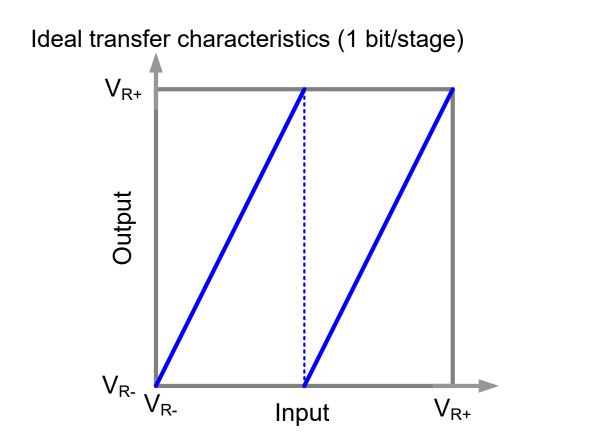

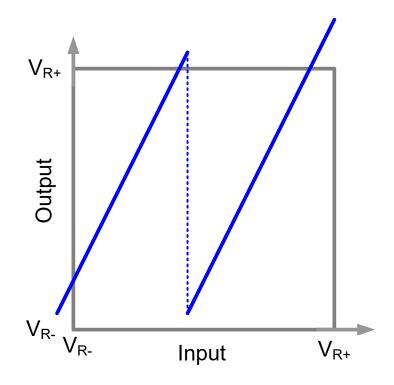

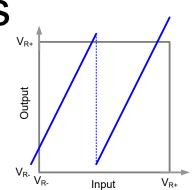

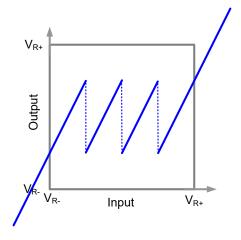

Ideal transfer characteristics (1 bit/stage)

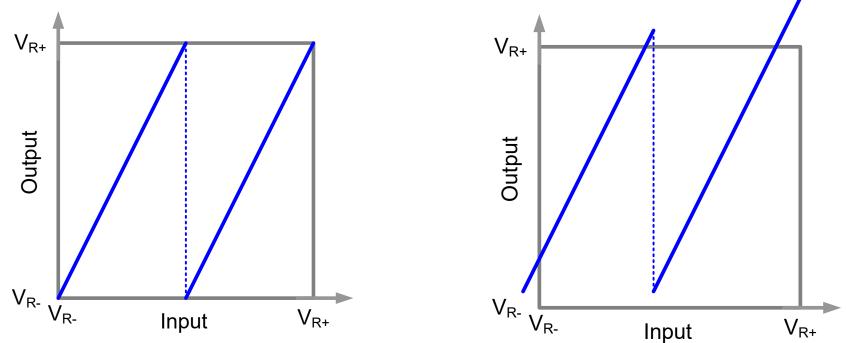

What are the effects of these errors?

Effects of Simultaneous Errors

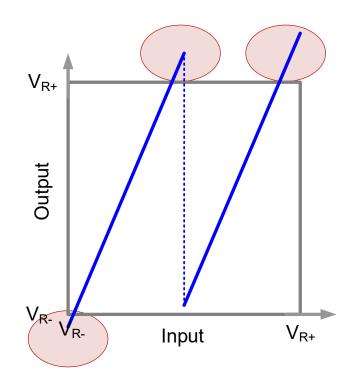

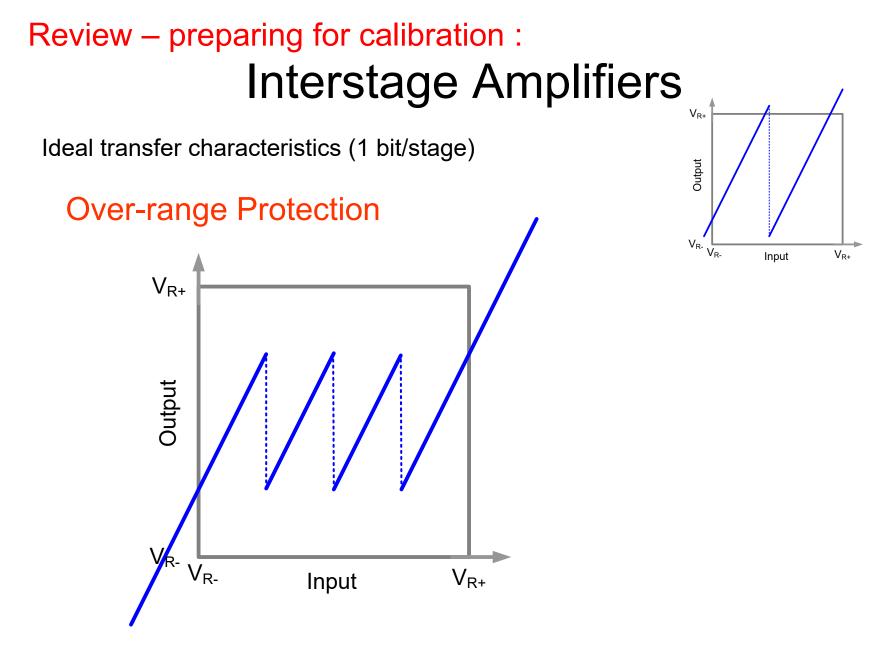

Ideal transfer characteristics (1 bit/stage)

What are the effects of these errors?

Extra comparator levels in ADC

Ideal transfer characteristics (1 bit/stage)

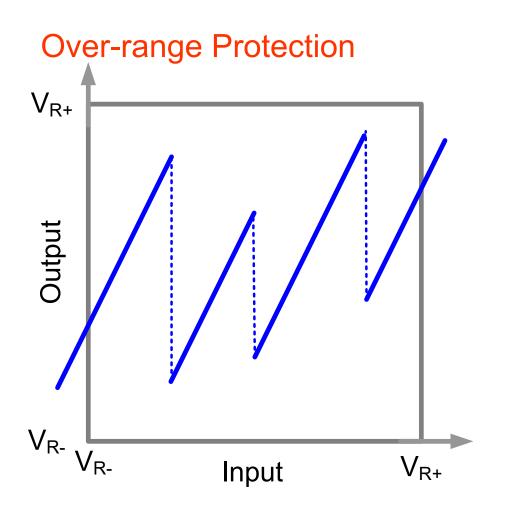

**Over-range Protection**

Extra comparator levels in ADC (1 extra comparator)

Extra comparator levels in ADC (2 extra comparators)

Ideal transfer characteristics (1 bit/stage)

Sub-radix Structure

# Pipelined Data Converter Design Guidelines

#### Issue

1. ADC offsets, Amp Offsets, Finite Op Amp Gain, DAC errors, Finite Gain Errors all cause amplifiers to saturate

### Strategy

- 1. Out-range protection circuitry will remove this problem and can make pipeline robust to these effects if  $\alpha_k$ 's correctly interpreted

- a) Use Extra Comparators

- b) Use sub-radix structures

# Pipelined Data Converter Design Guidelines

#### Issue

- 1. ADC offsets, Amp Offsets, Finite Op Amp Gain, DAC errors, Finite Gain Errors all cause amplifiers to saturate

- 2. Correct interpretation of  $\alpha_k$ 's is critical

### Strategy

- 1. Out-range protection circuitry will remove this problem and can make pipeline robust to these effects if  $\alpha_k$ 's correctly interpreted

- a) Use Extra Comparators

- b) Use sub-radix structures

- 2. a) Accurately set  $\alpha_k$  values

- b) Use analog or digital calibration

#### Performance Limitations of Pipelined ADCs (consider amplifier, ADC and DAC issues)

- Nonlinearity (primarily open loop)

- Open-loop

- ➡ Out-range

- → Gain Errors

- Inadequate open loop gain

- Component mismatch

- Power Dissipation

- kT/C switching noise

**X**<sub>OUTk</sub>

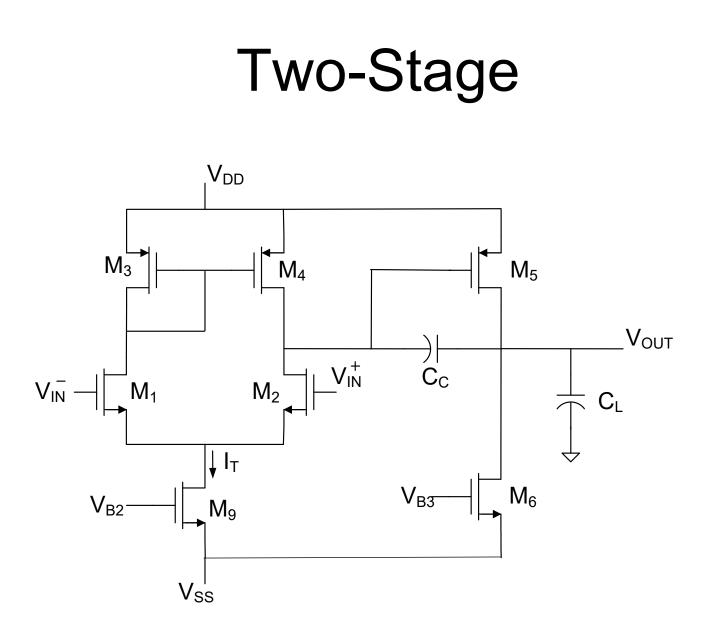

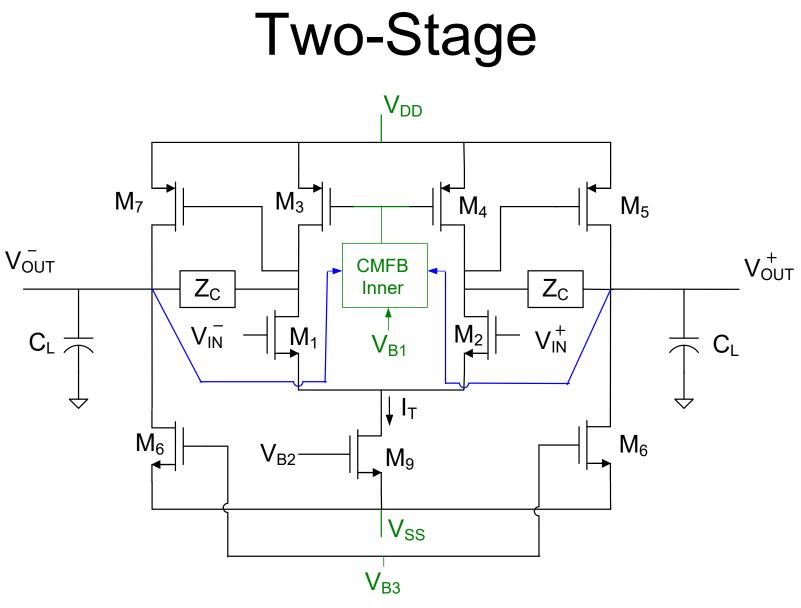

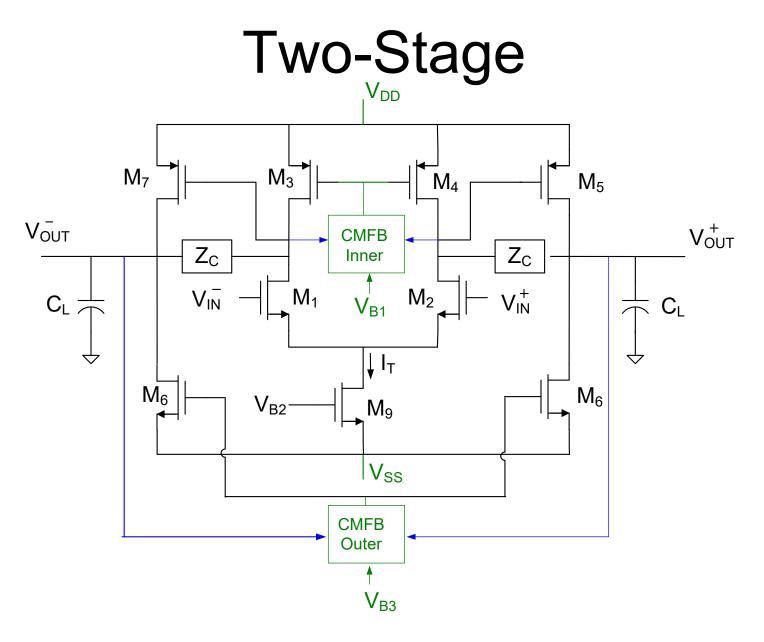

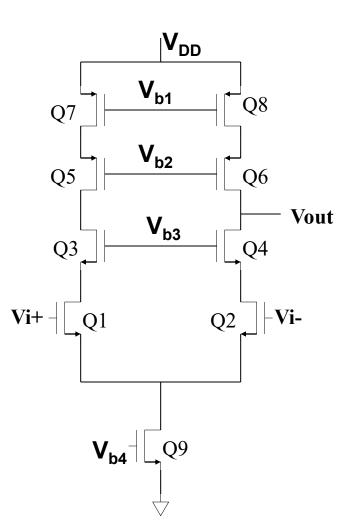

# Amplifier Types used In Pipelined ADCs

- Two-stage

- Cascode

- Telescopic

- Folded

- Regulated Cascode (Gain-boosted Cascode)

- Telescopic

- Folded

- Regenerative Feedback Gain Enhancement

- Two-Stage Cascode

Single-Ended Output

**Fully Differential**

29

**Fully Differential**

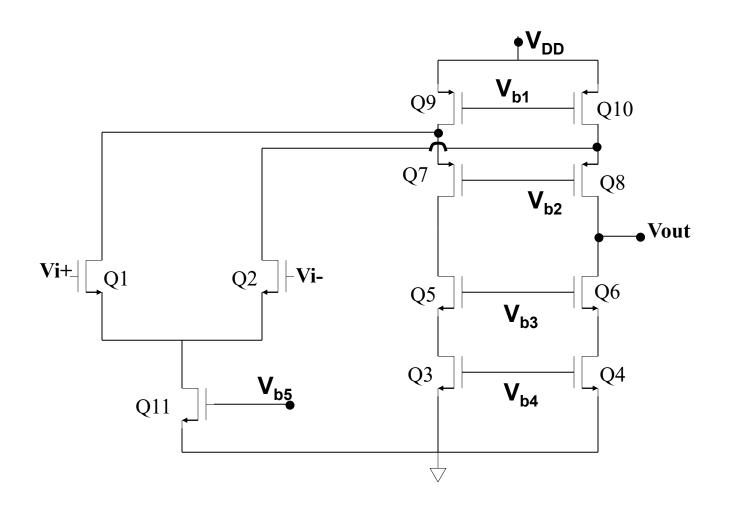

# **Telescopic Cascode**

**CMFB** Not Shown

## **Folded Cascode Amplifier**

**CMFB** Not Shown

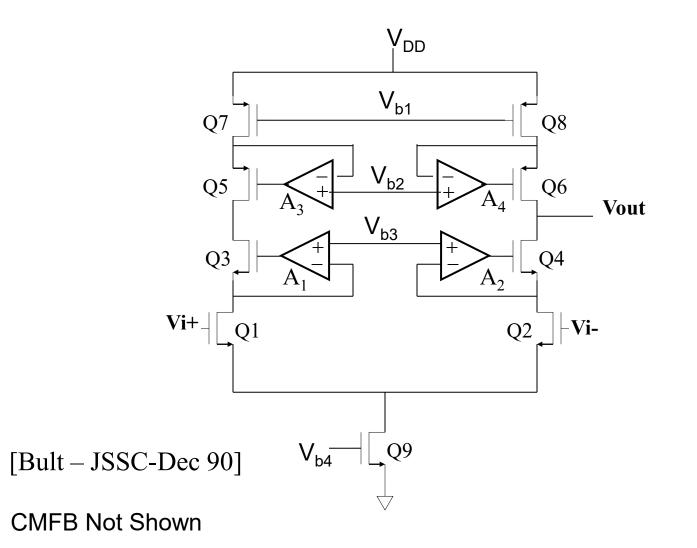

## Gain-Boosted Telescopic Cascode

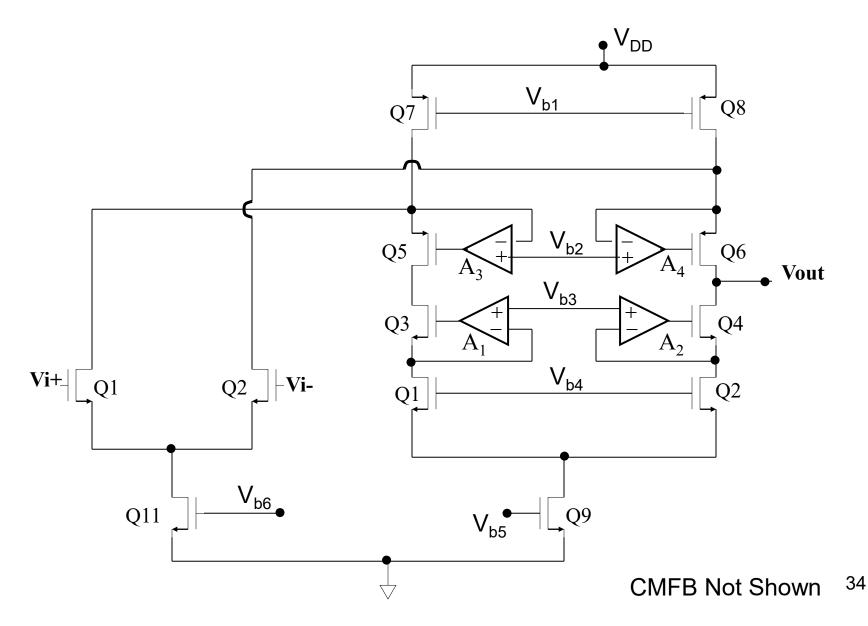

## Gain-Boosted Folded Cascode

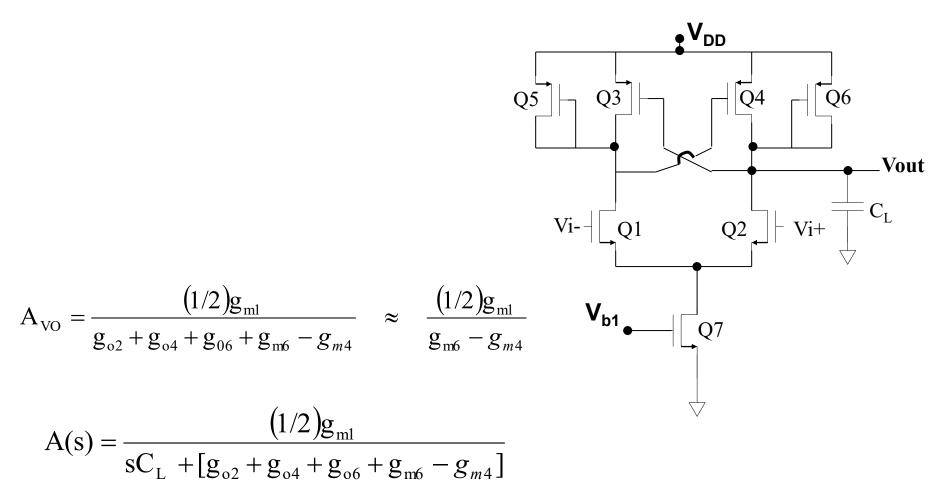

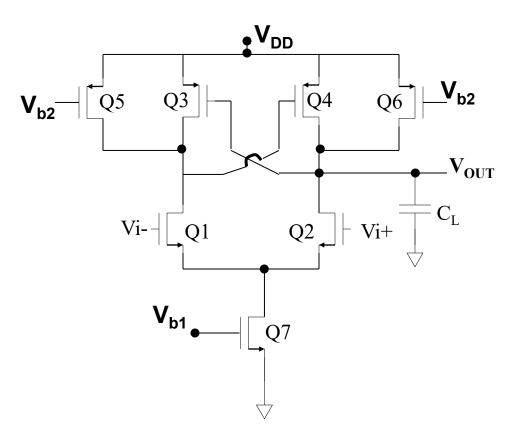

## -g<sub>m</sub> Compensation Implementation

# -gm Compensated Single-Stage

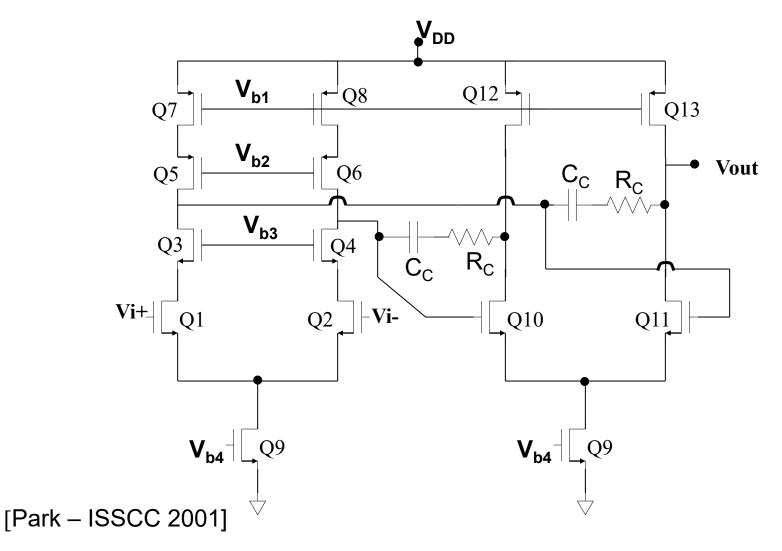

# Two-Stage Cascode/Cascade

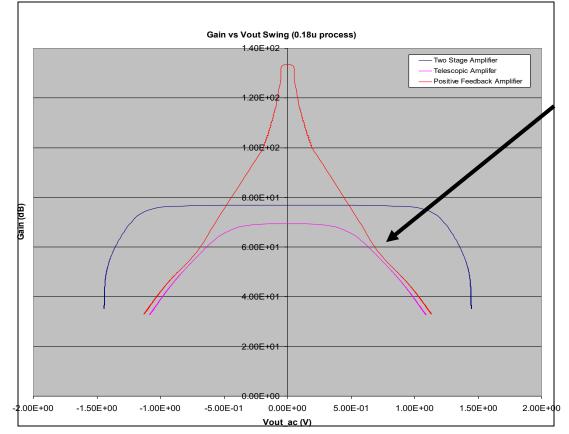

## Amplifier Nonlinearity Becoming Increasingly Significant as V<sub>DD</sub> Reduced

Comparison of amplifiers at same power

#### level and same $V_{EB}$

Drop in gain seriously degrades linearity and spectral performance

- Nonlinearity strongly architecture dependent

- Trade-Offs between Gain and Signal Swing

### How Much Gain?

Depends upon how much of the overall error budget is allocated to the effect noninfinite gain has on required performance parameters

If require n ENOB, can ½ LSB be allocated to effects of op amp gain error?

e.g. If INL specification of a 12-bit ADC is  $\frac{1}{2}$  LSB, can  $\frac{1}{2}$  LSB be allocated to the noninfinite gain error?

Sources that may contribute to INL errors in pipelined ADC:

Finite Op Amp Gain Capacitor Missmatch Incomplete amplifier settling Amplifier nonlinearity Input S/H error Parasitic capacitance nonlinearity Offset voltage (in ADC, DAC, summer) DAC errors ADC nonlinaritry

### **Error Budgeting**

Sources that may contribute to INL errors in pipelined ADC:

Finite Op Amp Gain Capacitor Missmatch Incomplete amplifier settling Amplifier nonlinearity Input S/H error Parasitic capacitance nonlinearity Offset voltage (in ADC, DAC, summer) DAC errors ADC nonlinaritry

If entire error budget (e.g. ½ LSB) is allocated to the Finite Op Amp Gain, what error budget must be allocated to all remaining contributors?

What will happen if each error source is allocated an error budget of (e.g. ½ LSB)?

How should the error sources contribution to overall error budget be allocated?

$$\sum_{i=1}^{m} e_i = \frac{1}{2} LSB \quad \text{(maybe a little bit overly conservative)}$$

40

### What type of error budget is used by industry?

Is ENOB equal to the specified number of bits of resolution?

Is it easy to add one additional ENOB of resolution to a given design ?

Why is the ENOB often less than the specified number of bits?

Will consider one example only, others may have ENOB closer or farther from specified resolution

### INL-based ENOB ENOB = $n_R$ -1-log<sub>2</sub>(v)

Consider an ADC with specified resolution of  $n_R$  and INL of v LSB

| V   | ENOB              |

|-----|-------------------|

| 1/2 | n <sub>R</sub>    |

| 1   | n <sub>R</sub> -1 |

| 2   | n <sub>R</sub> -2 |

| 4   | n <sub>R</sub> -3 |

| 8   | n <sub>R</sub> -4 |

| 16  | n <sub>R</sub> -5 |

Though based upon the continuous-INL definition, often used to define ENOB from INL v

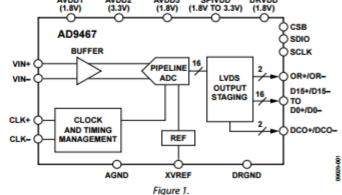

#### 16-Bit, 200 MSPS/250 MSPS Analog-to-Digital Converter

#### Data Sheet

#### \$120 in 1000's

$\log_2(3.5)=1.85$

#### AD9467

#### FEATURES

75.5 dBFS SNR to 210 MHz at 250 MSPS 90 dBFS SFDR to 300 MHz at 250 MSPS SFDR at 170 MHz at 250 MSPS 92 dBFS at -1 dBFS 100 dBFS at -2 dBFS

60 fs rms jitter Excellent linearity at 250 MSPS

$DNL = \pm 0.5 LSB typical$

INL = ±3.5 LSB typical

2 V p-p to 2.5 V p-p (default) differential full-scale

input (programmable)

Integrated input buffer

External reference support option

Clock duty cycle stabilizer

Output clock available

Serial port control

Built-in selectable digital test pattern generation

Selectable output data format

LVDS outputs (ANSI-644 compatible)

1.8 V and 3.3 V supply operation

#### APPLICATIONS

Multicarrier, multimode cellular receivers Antenna array positioning Power amplifier linearization Broadband wireless Radar Infrared imaging Communications instrumentation

#### FUNCTIONAL BLOCK DIAGRAM

#### ENOB = $n_{R}$ -1- $log_{2}(v)$ = 16-1-1.85 $\approx$ 13.15

### Is this close to 16-bit performance?

A data clock output (DCO) for capturing data on the output is provided for signaling a new output bit.

The internal power-down feature supported via the SPI typically consumes less than 5 mW when disabled.

Optional features allow users to implement various selectable operating conditions, including input range, data format select, and output data test patterns.

The AD9467 is available in a Pb-free, 72-lead, LFCSP specified over the -40°C to +85°C industrial temperature range.

#### Can we depend on this "13-bit" INL performance?

#### SPECIFICATIONS

AVDD1 = 1.8 V, AVDD2 = 3.3 V, AVDD3 = 1.8 V, DRVDD = 1.8 V, specified maximum sampling rate, 2.5 V p-p differential input, 1.25 V internal reference, AIN = -1.0 dBFS, DCS on, default SPI settings, unless otherwise noted.

| Table 1.                                                         |      |      |           |      |         |                                        |

|------------------------------------------------------------------|------|------|-----------|------|---------|----------------------------------------|

| Parameter <sup>1</sup>                                           | Temp | Min  | Тур       | Max  | Unit    |                                        |

| RESOLUTION                                                       |      | 16   |           |      | Bits    |                                        |

| ACCURACY                                                         |      |      |           |      |         |                                        |

| No Missing Codes                                                 | Full |      | Guarantee | d    |         |                                        |

| Offset Error                                                     | Full | -200 | 0         | +200 | LSB     |                                        |

| Gain Error                                                       | Full | -3.9 | -0.1      | +2.6 | %FSR    |                                        |

| Differential Nonlinearity (DNL) <sup>2</sup>                     | Full | -0.9 | ±0.5      | +1.5 | LSB     | $\log_2(12)=3.58$                      |

| Integral Nonlinearity (INL) <sup>2</sup>                         | Full | -12  | ±3.5      | +12  | LSB     | ······································ |

| TEMPERATURE DRIFT                                                |      |      |           |      |         |                                        |

| Offset Error                                                     | Full |      | ±0.023    |      | %FSR/°C |                                        |

| Gain Error                                                       | Full |      | ±0.036    |      | %FSR/°C |                                        |

| ANALOG INPUTS                                                    |      |      |           |      |         |                                        |

| Differential Input Voltage Range (Internal VREF = 1 V to 1.25 V) | Full | 2    | 2.5       | 2.5  | V p-p   |                                        |

| Common-Mode Voltage                                              | 25°C |      | 2.15      |      | V       |                                        |

| Differential Input Resistance                                    | 25°C |      | 530       |      | Ω       |                                        |

| Differential Input Capacitance                                   | 25°C |      | 3.5       |      | pF      |                                        |

| Full Power Bandwidth                                             | 25°C |      | 900       |      | MHz     |                                        |

| XVREF INPUT                                                      |      |      |           |      |         |                                        |

| Input Voltage                                                    | Full | 1    |           | 1.25 | V       |                                        |

| Input Capacitance                                                | Full |      | 3         |      | pF      |                                        |

| POWER SUPPLY                                                     |      |      |           |      |         |                                        |

| AVDD1                                                            | Full | 1.75 | 1.8       | 1.85 | V       |                                        |

| AVDD2                                                            | Full | 3.0  | 3.3       | 3.6  | V       |                                        |

| AVDD3                                                            | Full | 1.7  | 1.8       | 1.9  | V       |                                        |

| DRVDD                                                            | Full | 1.7  | 1.8       | 1.9  | V       |                                        |

| I <sub>AVD1</sub>                                                | Full |      | 567       | 620  | mA      |                                        |

| AVDD2                                                            | Full |      | 55        | 61   | mA      |                                        |

| I <sub>AVDD3</sub>                                               | Full |      | 31        | 35   | mA      |                                        |

| I <sub>DRVDD</sub>                                               | Full |      | 40        | 43   | mA      |                                        |

| Total Power Dissipation (Including Output Drivers)               | Full |      | 1.33      | 1.5  | W       |                                        |

| Power-Down Dissipation                                           | Full |      | 4.4       | 90   | mW      |                                        |

<sup>1</sup> See the AN-835 Application Note, Understanding High Speed ADC Testing and Evaluation, for a complete set of definitions and how these tests were completed. <sup>2</sup> Measured with a low input frequency, full-scale sine wave, with approximately 5 pF loading on each output bit.

ENOB =  $n_{R}$ -1-log<sub>2</sub>(v) = 16-1-3.58  $\approx$  11.42

From INL viewpoint, performance of marketed parts could be about 4.5 bits less than physical resolution but does have other attractive properties

#### AC SPECIFICATIONS

AVDD1 = 1.8 V, AVDD2 = 3.3 V, AVDD3 = 1.8 V, DRVDD = 1.8 V, specified maximum sampling rate, 2.5 V p-p differential input, 1.25 V internal reference, AIN = -1.0 dBFS, DCS on, default SPI settings, unless otherwise noted.

| Parameter <sup>1</sup>                                                              | Temp | Min  | Typ Max   | Unit |

|-------------------------------------------------------------------------------------|------|------|-----------|------|

| ANALOG INPUT FULL SCALE                                                             |      | 2.5  | 2/2.5     | Vp-p |

| SIGNAL-TO-NOISE RATIO (SNR)                                                         |      |      |           |      |

| $f_{IN} = 5 MHz$                                                                    | 25°C |      | 74.7/76.4 | dBFS |

| $f_{\rm H} = 97  \rm MHz$                                                           | 25°C |      | 74.5/76.1 | dBFS |

| $f_{\rm IN} = 140  \rm MHz$                                                         | 25°C |      | 74.4/76.0 | dBFS |

| f <sub>N</sub> = 170 MHz                                                            | 25°C | 73.7 | 74.3/75.8 | dBFS |

|                                                                                     | Full | 71.5 |           | dBFS |

| f <sub>N</sub> = 210 MHz                                                            | 25°C |      | 74.0/75.5 | dBFS |

| f <sub>N</sub> = 300 MHz                                                            | 25°C |      | 73.3/74.6 | dBFS |

| SIGNAL-TO-NOISE AND DISTORTION RATIO (SINAD)                                        |      |      |           |      |

| f <sub>IN</sub> = 5 MHz                                                             | 25°C |      | 74.6/76.3 | dBFS |

| f <sub>N</sub> = 97 MHz                                                             | 25°C |      | 74.4/76.0 | dBFS |

| f <sub>N</sub> = 140 MHz                                                            | 25°C |      | 74.4/76.0 | dBFS |

| $f_{\rm IN} = 170 \rm MHz$                                                          | 25°C | 72.4 | 74.2/75.8 | dBFS |

|                                                                                     | Full | 71.0 |           | dBFS |

| f <sub>N</sub> = 210 MHz                                                            | 25°C |      | 73.9/75.4 | dBFS |

| TN = 300 MHz                                                                        | 25°C |      | /3.1//4.4 | OBES |

| EFFECTIVE NUMBER OF BITS (ENOB)                                                     |      |      |           |      |

|                                                                                     | 25°C |      | 12.1/12.4 | Bits |

| $f_{N}=5 MHz$ • Can be defined different ways                                       | 25°C |      | 12.1/12.3 | Bits |

| · · · · · · · · · · · ·                                                             | 25°C |      | 12.1/12.3 | Bits |

| $f_{N} = 140 \text{ MHz}$ • Only given as typical                                   | 25°C |      | 12.0/12.3 | Bits |

|                                                                                     | Full | 11.5 |           | Bits |

| f <sub>N=210 MHz</sub> • Only specified at 25C                                      | 25°C |      | 12.0/12.2 | Bits |

| f <sub>N</sub> = 300 MHz                                                            | 25°C |      | 11.9/12.1 | Bits |

| SPURIOUS-FREE DYNAMIC RANGE (SFDR) (INCLUDING SECOND AND THIRD HARMONIC DISTORTION) |      |      |           |      |

| f <sub>IN</sub> = 5 MHz                                                             | 25°C |      | 98/97     | dBFS |

| fn = 97 MHz                                                                         | 25°C |      | 95/93     | dBFS |

| f <sub>N</sub> = 140 MHz                                                            | 25°C |      | 94/95     | dBFS |

| f <sub>N</sub> = 170 MHz                                                            | 25°C | 82   | 93/92     | dBFS |

|                                                                                     | Full | 82   |           | dBFS |

| $f_{\rm H} = 210  \rm MHz$                                                          | 25°C |      | 93/92     | dBFS |

| f <sub>N</sub> = 300 MHz                                                            | 25°C |      | 93/90     | dBFS |

| SFDR (INCLUDING SECOND AND THIRD HARMONIC DISTORTION)                               |      |      |           |      |

| fn = 5 MHz at -2 dB Full Scale                                                      | 25°C |      | 100/100   | dBFS |

| $f_N = 97 \text{ MHz at} - 2 \text{ dB Full Scale}$                                 | 25°C |      | 97/97     | dBFS |

| f <sub>N</sub> = 140 MHz at-2 dB Full Scale                                         | 25°C |      | 100/95    | dBFS |

| $f_{\rm N} = 170 \rm MHz$ at $-2 \rm dB$ Full Scale                                 | 25°C |      | 100/100   | dBFS |

| $f_N = 210 \text{ MHz at} - 2 \text{ dB Full Scale}$                                | 25°C |      | 93/93     | dBFS |

| $f_N = 300 \text{ MHz}$ at $-2 \text{ dB}$ Full Scale                               | 25°C |      | 90/90     | dBFS |

| WORST OTHER (EXCLUDING SECOND AND THIRD HARMONIC DISTORTION)                        |      |      |           |      |

| $f_N = 5 \text{ MHz}$                                                               | 25°C |      | 98/97     | dBES |

| $f_N = 97 \text{ MHz}$                                                              | 25°C |      | 97/93     | dBFS |

| $f_N = 140 \text{ MHz}$                                                             | 25°C |      | 97/95     | dBFS |

| $f_{\rm N} = 140 \text{ MHz}$<br>$f_{\rm N} = 170 \text{ MHz}$                      | 25°C | 88   | 97/93     | dBFS |

| 18 = 170 Milz                                                                       | Full | 82   | 21123     | dBFS |

|                                                                                     | Full | 02   |           |      |

| f <sub>N</sub> = 210 MHz                                                            | 25°C |      | 97/95     | dBFS |

# How Much Gain?

Conventional Approach: Assume want to make at most  $\frac{1}{2}$  LSB error in closed loop gain at each stage

Often see authors use

$$A_{_{\scriptscriptstyle \mathrm{dB}}}\cong 6n_{_{\scriptscriptstyle \mathrm{ST}}}+12$$

- Gives no information about drop in gain at boundary of input/output window

- Not dependent upon architecture ?

- Maybe uses too much error budget on gain

- Errors accumulate since gain errors will exist on each stage

- No indication how A<sub>dB</sub> relates to INL or DNL

- Gain requirements are large on the input buffer ( $n_{ST}=n$ ) but will be significantly relaxed on latter stages in the pipeline when  $n_{ST}$  decreases

## Pipelined Data Converter Design Guidelines

#### Issue

- 1. ADC offsets, Amp Offsets, Finite Op Amp Gain, DAC errors, Finite Gain Errors all cause amplifiers to saturate

- 2. Op Amp Gain causes finite gain errors and introduces noninearity

### Strategy

- 1. Out-range protection circuitry will remove this problem and can make pipeline robust to these effects if  $\alpha_k$ 's correctly interpreted

- a) Use Extra Comparators

- b) Use sub-radix structures

- 2. a) Select op amp architecture that has acceptable signal swing

b) Select gain large enough at boundary of range to minimize nonlinearity and gain errors

### Performance Limitations of Pipelined ADCs (consider amplifier, ADC and DAC issues)

- Nonlinearity (primarily open loop)

- ➡ Open-loop

- → Out-range

- → Gain Errors

$\implies$  ADC

DAC

- Inadequate open loop gain

- Component mismatch

- Power Dissipation

- kT/C switching noise

**X**<sub>OUTk</sub>

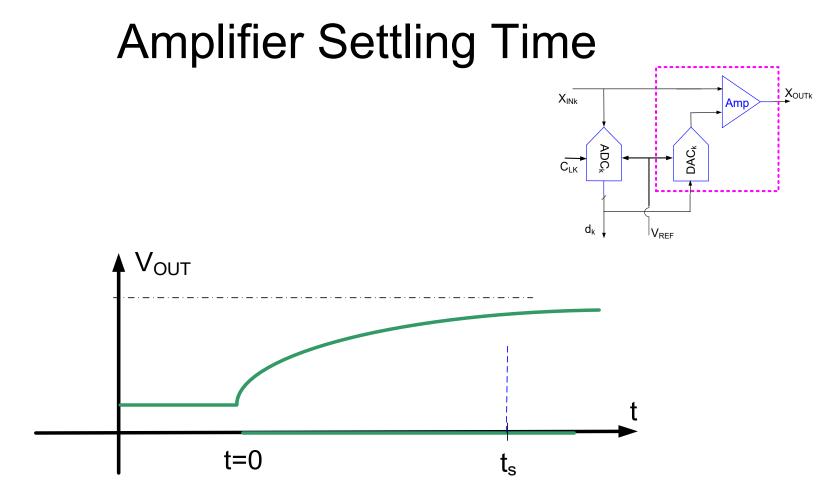

- Can show that no distortion is introduced in pipelined ADC if the amplifier settling is linear (i.e. don't worry about incomplete settling)

- But invariably slew rate and op amp nonlinearities will cause settling to be nonlinear

- Since can't guarantee linear settling, must design for complete settling

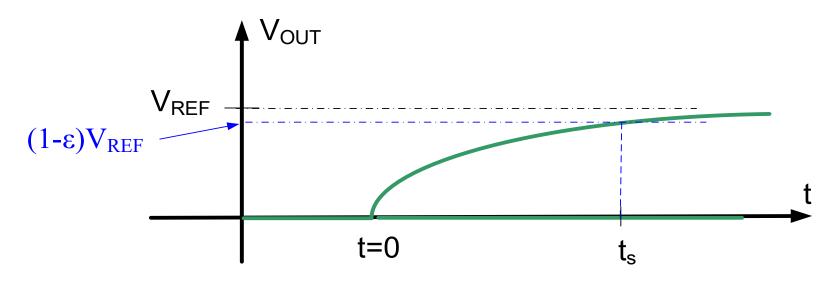

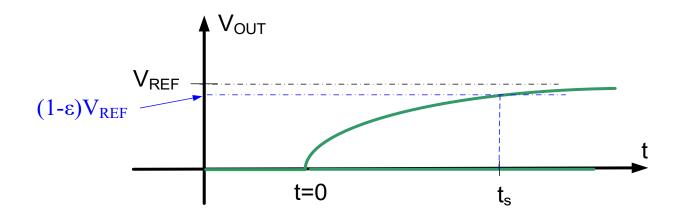

### **Amplifier Settling Time**

### Worst Case Settling

- Neglect over-range protection (could be up against over-range limit)

- Occurs when input causes <u>output</u> to swing from 0 to V<sub>REF</sub>

Conventional Approach: Assume want to make at most ½ LSB error in settling for worst-case step on output in each stage

Note: This may not be quite good enough since allocating total error budget to settling of each stage

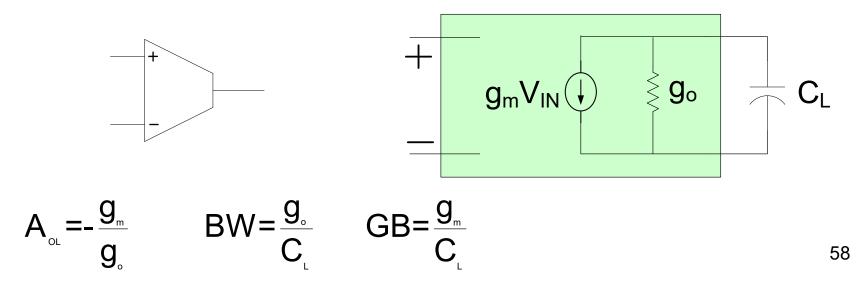

Compensated Operational Amplifier can be approximately modeled by

$$\mathsf{A}_{_{OL}}(s) \cong \frac{\mathsf{A}_{_{o}}\mathsf{p}_{_{_{F}}}}{\mathsf{s+p}_{_{_{F}}}} = \frac{\mathsf{G}\mathsf{B}}{\mathsf{s+p}_{_{_{F}}}}$$

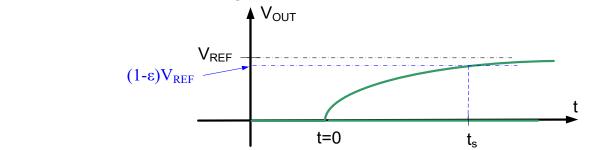

Conventional Approach: Assume want to make at most ½ LSB error in settling for worst-case step in each stage

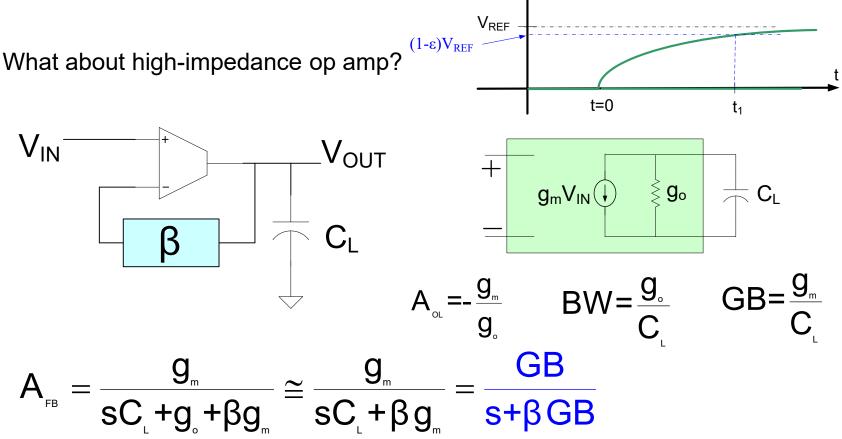

$$A_{OL}(s) \cong \frac{A_{O}p_{OL}}{s+p_{OL}} = \frac{GB}{s+p_{OL}} \qquad A_{FB}(s) = \frac{A_{O}p_{OL}}{s+p_{OL}+\beta A_{O}p_{OL}} \cong \frac{GB}{s+\beta GB}$$

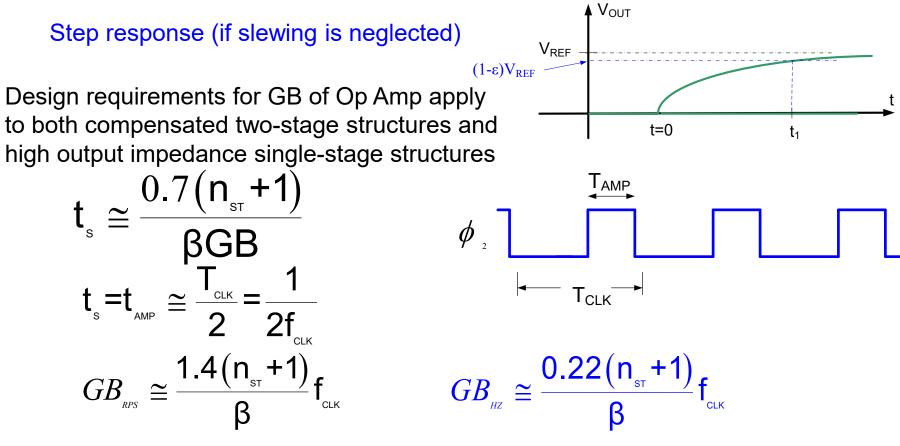

Step response (if slewing is neglected and dc gain large)

$$r(t) = F + (I - F) e^{-\beta GBt_{s}}$$

$$V_{REF} (1 - \varepsilon) = V_{REF} (1 - e^{-\beta GBt_{s}})$$

$$1 - \varepsilon = 1 - e^{-\beta GBt_{s}}$$

$$\varepsilon = e^{-\beta GBt_{s}}$$

$$t_{s} = -\frac{\ln(\varepsilon)}{\beta GB}$$

or, in terms of the time constant  $\tau$  of closed loop amplifier

$$\mathbf{t}_{s} = -\tau \ln(\varepsilon)$$

<sup>54</sup>

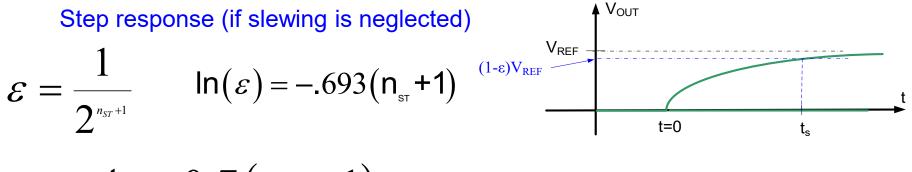

Conventional Approach: Assume want to make at most ½ LSB error in settling for worst-case step in each stage

Define  $n_{ST}$  to be the number of bits of resolution at the residue output of a stage

$$\mathbf{t}_{s} \cong 0.7 (n_{s\tau} + 1) \tau$$

- linear increase in settling requirements with n<sub>ST</sub>

- n<sub>ST</sub> determined by accuracy requirements at residue output of a stage

Still need design requirements for GB of Op Amp

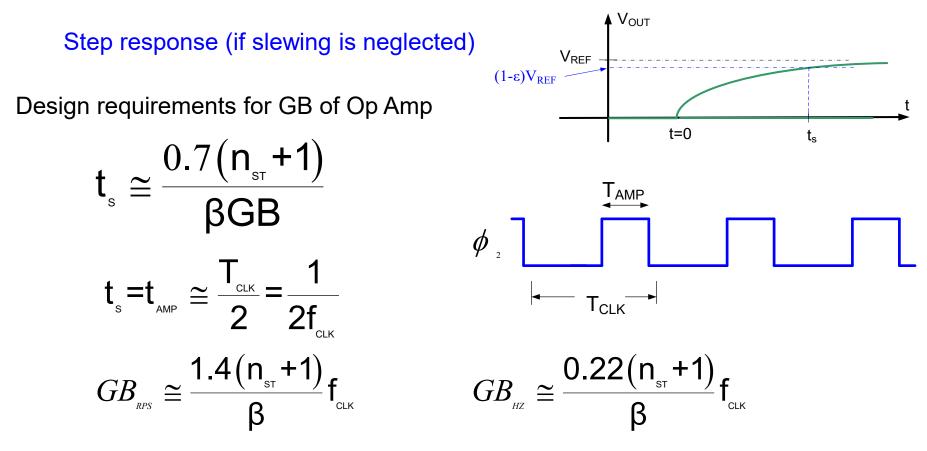

$$\mathsf{t}_{_{\mathrm{s}}} \cong \frac{0.7(\mathsf{n}_{_{\mathrm{s}\mathrm{T}}}+1)}{\beta \mathsf{GB}}$$

Conventional Approach: Assume want to make at most ½ LSB error in settling for worst-case step in each stage

Note: GB requirements drop from stage to stage

Conventional Approach: Assume want to make at most ½ LSB error in settling for worst-case step in each stage

Compensated Operational Amplifier can be approximately modeled by

$$A(s) \cong \frac{A_{o}p_{F}}{s+p_{F}} = \frac{GB}{s+p_{F}}$$

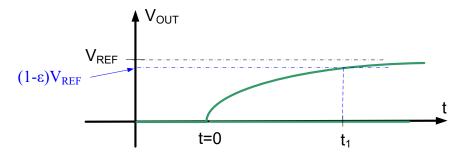

What about high-impedance op amp?

Conventional Approach: Assume want to make at most ½ LSB error in settling for worst-case step at each stage

What about high-impedance op amp driving capacitive load (including  $\beta$  network)?

Conventional Approach: Assume want to make at most ½ LSB error in settling for worst-case step

Note this is identical in form to that from the internally compensated op amp <sup>59</sup>

Conventional Approach: Assume want to make at most ½ LSB error in settling for worst-case step

60

Notes: May be over-using error budget Slewing will modestly slow response

## Pipelined Data Converter Design Guidelines

#### Issue

1. ADC offsets, Amp Offsets, Finite Op Amp Gain, DAC errors, Finite Gain Errors all cause amplifiers to saturate

2. Op Amp Gain causes finite gain errors and introduces noninearity

3. Op amp settling must can cause errors

### Strategy

- 1. Out-range protection circuitry will remove this problem and can make pipeline robust to these effects if  $\alpha_k$ 's correctly interpreted

- a) Use Extra Comparators

- b) Use sub-radix structures

- 2. a) Select op amp architecture that has acceptable signal swing

b) Select gain large enough at boundary of range to minimize nonlinearity and gain errors

3. Select GB to meet settling requirements (degrade modestly to account for slewing)

### Performance Limitations of Pipelined ADCs (consider amplifier, ADC and DAC issues)

- Nonlinearity (primarily open loop)

- → Open-loop

- → Out-range

- → Gain Errors

→ ADC

DAC

- Inadequate open loop gain

- Component mismatch

- Power Dissipation

- kT/C switching noise

**X**<sub>OUTk</sub>

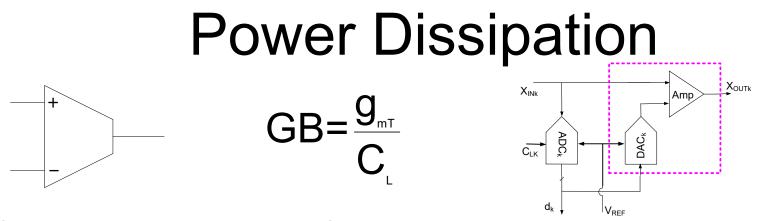

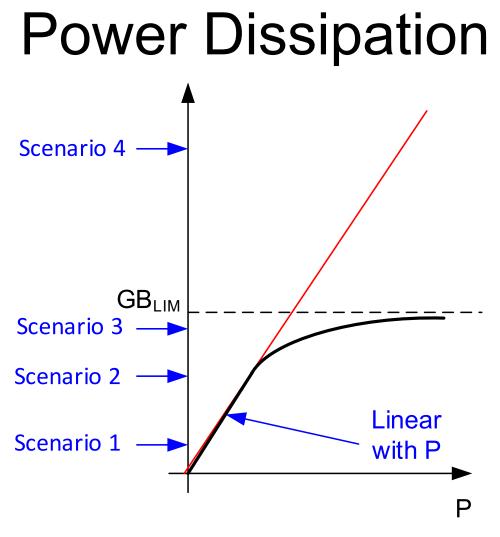

## **Power Dissipation**

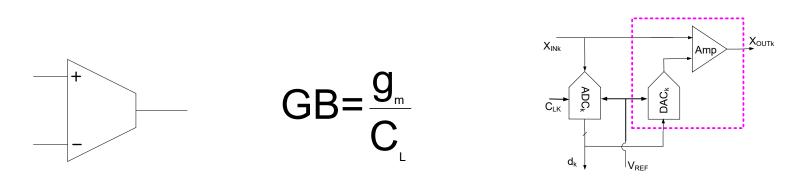

### Dominant source of power dissipation is in the op amps in S/H and individual stages

# **Power Dissipation**

- Power dissipation strongly dependent upon op amp architecture and design

- Power budgets critical and even a net 5% savings in power is significant!

Consider a single stage in the pipeline

Consider single stage open-loop op amp structures (e.g. telescopic cascode)

$$A_{OL} = -\frac{g_{mT}}{g_{OT}} \qquad P_{OP AMP} \cong 2I_{DQ} \left( \bigvee_{DD} - \bigvee_{SS} \right)$$

Power increases linearly with  $I_{DQ}$

For MOS implementation with basic reference SE op amp

$$= -\frac{2I_{DQ}}{V_{EB}} \frac{1}{2\lambda I_{DQ}} = -\frac{1}{\lambda V_{EB}}$$

No power implications on dc gain of op amp

$$\cdot \text{ Pick } V_{EB} \text{ small to increase gain}$$

$$\cdot \text{ Pick } V_{EB} \text{ small to increase gain}$$

$C_L$  is the parallel combination of any interconnect capacitance, the capacitance of the  $\beta$  network and the sampling capacitance of the following stage

For MOS implementation (with ref SE op amp or telescopic cascode op amp)

$$GB = \frac{2I_{DQ}}{V_{EB}C_{L}} = \left(\frac{1}{(V_{DD}-V_{SS})}\frac{P}{C_{L}}\right)\frac{1}{V_{EB}}$$

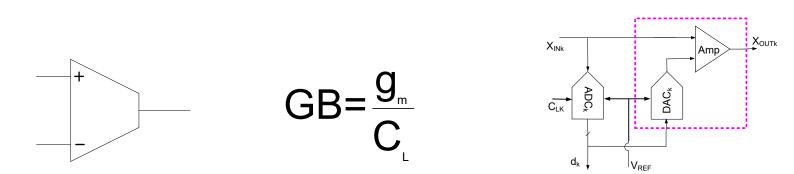

$$P = V_{SUP} \bullet GB \bullet C_{L} \bullet V_{EB}$$

For convenience, define

$$V_{SUP} = V_{DD} - V_{SS}$$

- Keep  $V_{EB}$  small,  $C_L$  as small as possible, GB as small as possible

- At high speeds, diffusion parasitics will cause P to increase more rapidly than GB

- Total amplifier power is sum of power in each stage

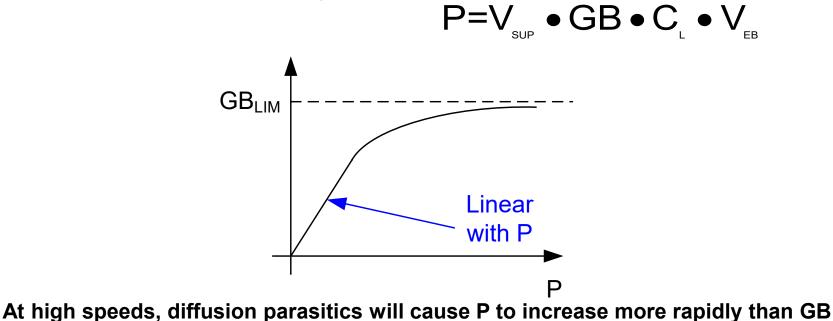

## **Power Dissipation**

For single-stage MOS implementation (with ref SE op amp or telescopic cascade op amp)

### **Power Dissipation**

Interleaving can dramatically reduce power requirements (e.g. two interleaved stages reduce GB requirements a factor of 2 on each stage thereby maintaining power requirements on linear slope region) for high speed data converters but introduces some calibration challenges

GB<sub>LIM</sub> strongly technology dependent

What do we do if system requirements are in the respective scenarios?

## **Power Dissipation**

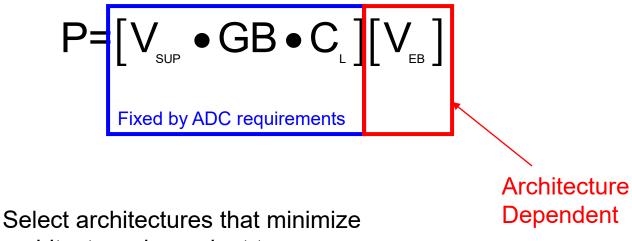

For Single-stage MOS implementation (with ref SE op amp or telescopic cascade op amp)

architecture-dependent term

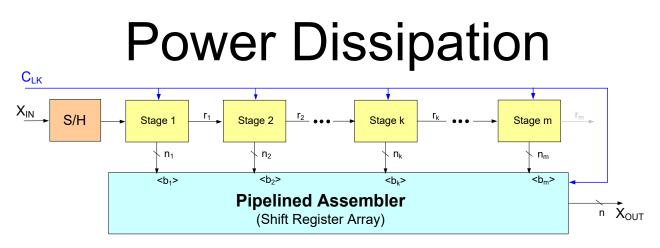

#### **Power Dissipation** CLK $X_{IN}$ $\mathbf{r}_1$ S/H Stage 1 Stage 2 Stage k Stage m $n_1$ $n_2$ n<sub>k</sub> n<sub>m</sub> <b<sub>2</sub>> <b⊧> <b\_> <b₁> **Pipelined Assembler** n X<sub>OUT</sub> (Shift Register Array)

For Single-stage MOS implementation (with ref SE op amp or telescopic cascade op

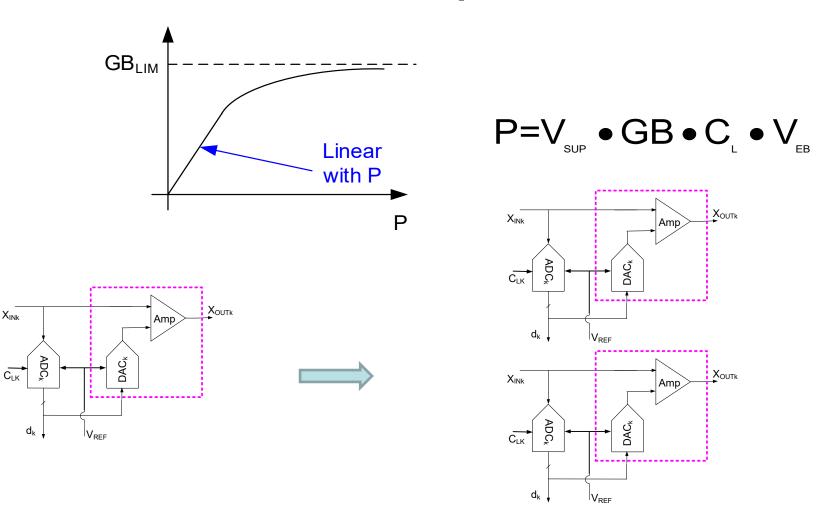

$$P = \begin{bmatrix} V_{SUP} \bullet GB \bullet C_{L} \end{bmatrix} \begin{bmatrix} V_{EB} \end{bmatrix} \qquad GB_{HZ} \cong \frac{0.22(n_{ST} + 1)}{\beta} f_{CLK}$$

Fixed by ADC requirements

- $n_{ST}$ =n for S/H thus S/H is a major power consumer

- Use energy efficient op amp architecture

- Power increases linearly with GB (even faster at high frequencies)

- Interleaving can reduce power dissipation at high frequencies( and extend effective clock speed)

- Power increases linearly with clock speed (or worse at high frequencies)

- Power can be scaled down in latter stages since  ${\rm n}_{\rm ST}$  will decrease

- Amplifiers can be shared between stages or switched off when not used (factor of 2!)

- Using more than one bit/stage will reduce power since no of op amps will decrease (offsets decrease in β)

- Elimination of S/H will have dramatic effect on power reduction

For Single-stage MOS implementation (with ref SE op amp or telescopic cascade op amp)

$$\mathsf{P} = \begin{bmatrix} \mathsf{V}_{\text{SUP}} \bullet \mathsf{GB} \bullet \mathsf{C}_{\text{L}} \end{bmatrix} \begin{bmatrix} \mathsf{V}_{\text{EB}} \end{bmatrix} \qquad GB_{\text{HZ}} \cong \frac{0.22(\mathsf{n}_{\text{sT}} + 1)}{\beta} \mathsf{f}_{\text{CLK}}$$

Fixed by ADC requirements

Which op amp architectures are most energy efficient?

- Depends upon  $\beta$

- For smaller  $\beta$ , two-stage are more energy efficient for larger  $\beta$  single-stage are better

- Must optimize power in any given architecture

- Folding reduces efficiency (typically by 30% to 50%)

## Stay Safe and Stay Healthy !

### End of Lecture 24

End of Lecture 21 From Spring 2019